Intel's make-or-break 18A process node debuts for data center with 288-core Xeon

Source: Hacker News

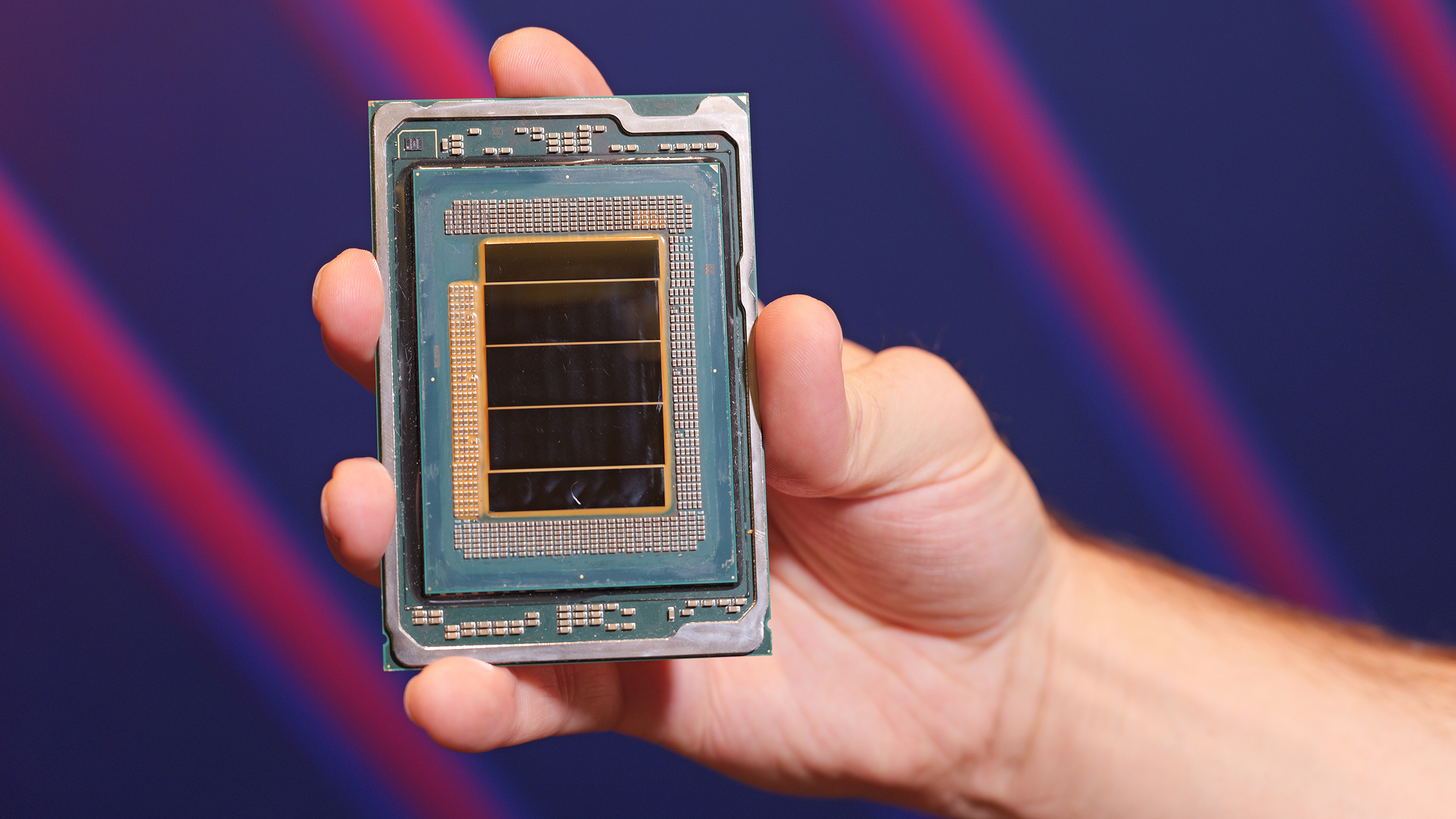

Image credit: Intel

Overview

Intel formally introduced its Xeon 6+ processors, codenamed Clearwater Forest, featuring up to 288 energy‑efficient Darkmont cores. These are the first data‑center CPUs manufactured on Intel’s 18A (1.8 nm‑class) fabrication process. The chips target telecom, cloud, and edge AI workloads and include Advanced Matrix Extensions (AMX), QuickAssist Technology (QAT), and Intel vRAN Boost.

Architecture Details

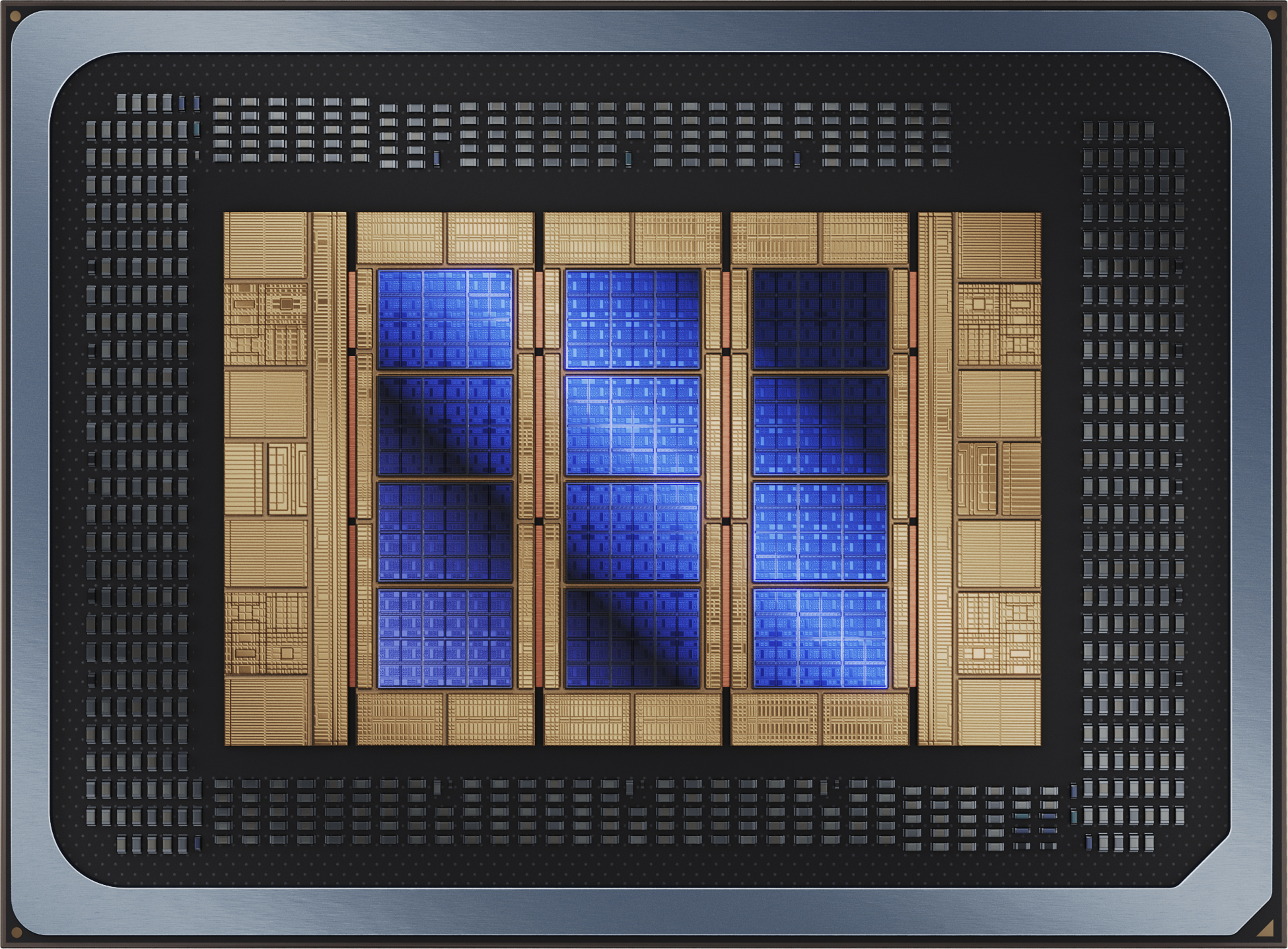

Image credit: Intel

-

Darkmont efficiency cores receive significant micro‑architectural upgrades:

- 64 KB L1 instruction cache per core

- Wider fetch and decode pipeline

- Deeper out‑of‑order engine with more in‑flight operations

- Increased number of execution ports for higher scalar and vector throughput

-

Cache hierarchy:

- Cores are grouped into four‑core blocks sharing ~4 MB of L2 cache each

- Total last‑level cache exceeds 1 GB (≈1,152 MB) across the full package, reducing reliance on external memory bandwidth and improving performance‑per‑watt

Platform and I/O

- Drop‑in compatible with the current Xeon server socket

- 12 memory channels supporting DDR5‑8000

- 96 PCIe 5.0 lanes, with 64 lanes supporting CXL 2.0

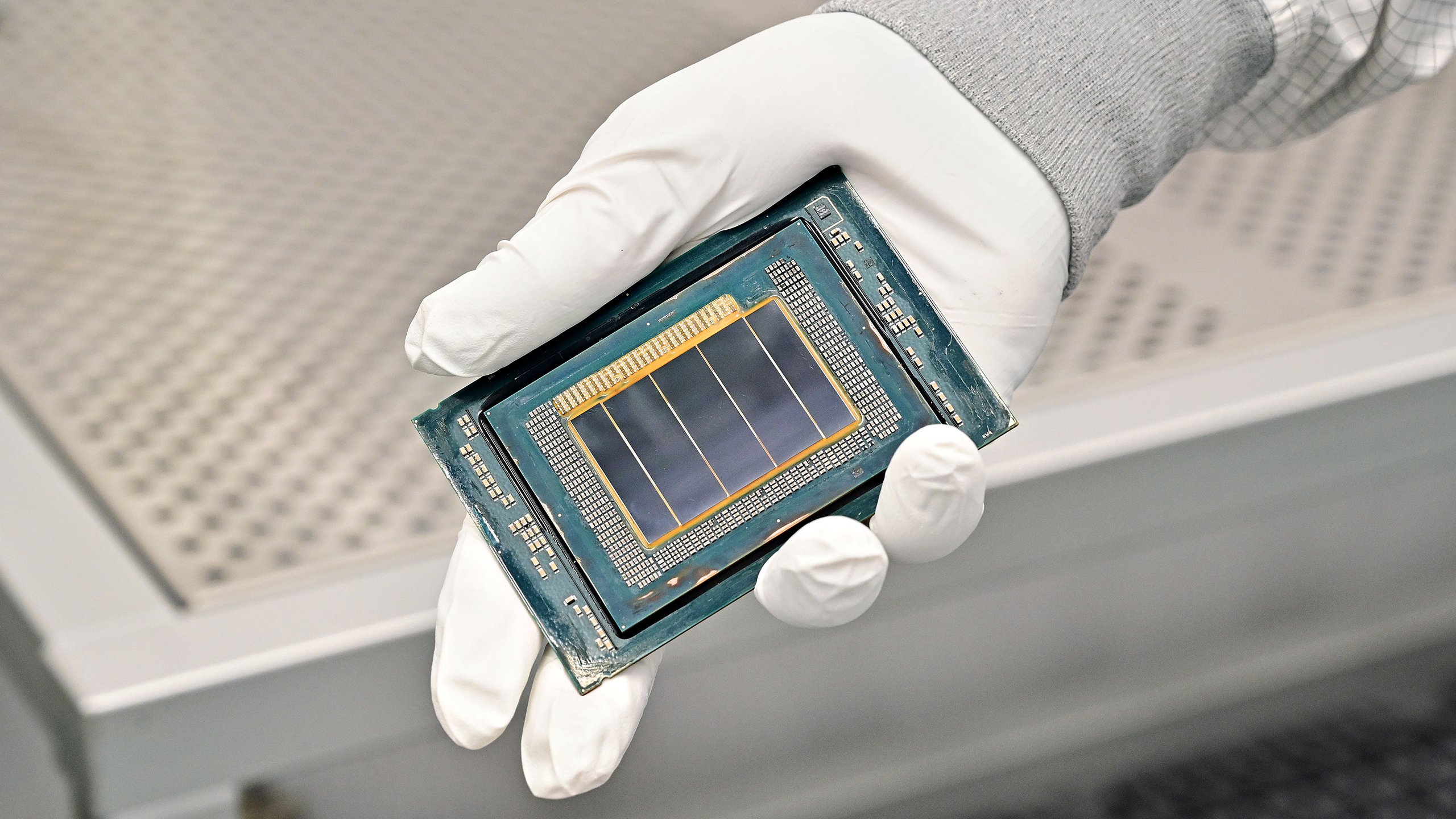

Image credit: Intel

Target Workloads

Intel positions Clearwater Forest for telecom and cloud environments, especially for:

- 5G Advanced and future 6G networks that rely on virtualized RAN (vRAN) and edge AI inference

- Scenarios where operators prefer CPUs over separate AI accelerators to avoid data‑center redesign

By integrating matrix/vector acceleration, vRAN offloads (via vRAN Boost), large caches, and extensive I/O, the CPU can handle tasks traditionally assigned to multiple accelerators, delivering lower power consumption and reduced footprint.

Core Count and Scalability

- Up to 288 cores in a single‑socket configuration

- Up to 576 cores in dual‑socket servers

- Enables a single server to host dozens or hundreds of virtual machines while maintaining power efficiency and low latency

Availability

Systems based on Intel’s Xeon 6+ processors are expected to be released later this year.