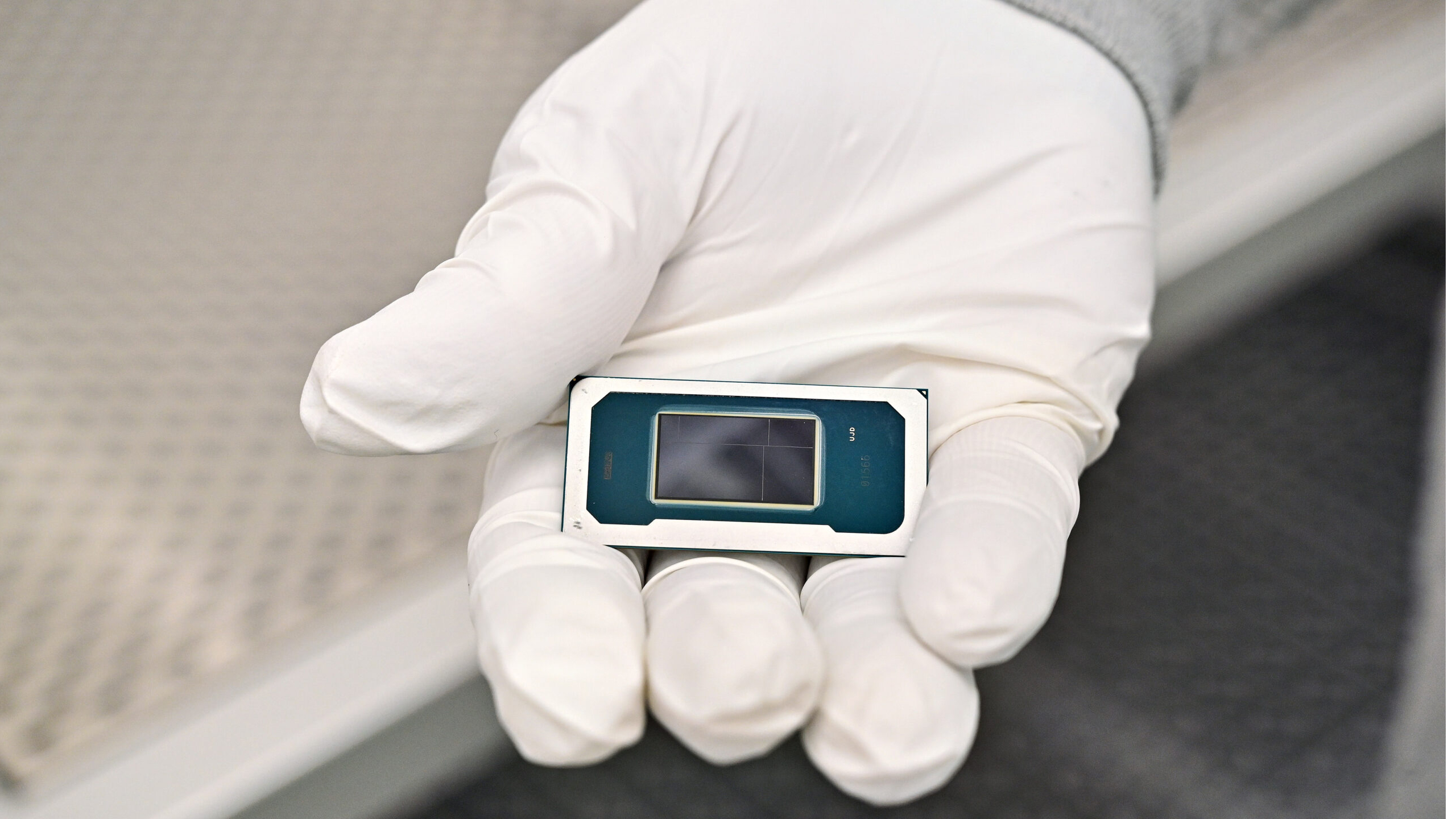

Intel Panther Lake-H high-res die shot emerges — image show 18A compute tile, Xe3 GPU tile in new X-series processors

Source: Tom’s Hardware

Image credit: Intel

Intel formally introduced its Core Ultra 300‑series processors (codenamed Panther Lake‑H) in January and has already shipped several SKUs to partners, but the die shots have not been publicly released—until now.

Kurnal‑Insights.com (run by @KurnalSalts) published annotated die shots of the three tiles that compose the Panther Lake‑H processor:

- Compute tile – fabricated on Intel’s 18 A process

- Xe3 graphics tile

- I/O tile

Compute Tile

The compute tile measures 14.32 × 8.04 × 0.18 mm and includes:

- CPU cores built on the 18 A node.

- Integrated media and display engines, allowing the tile to retain key functionality even when paired with various GPU and I/O dies.

- 128‑bit DDR5/LPDDR5X‑9600 memory controller with an 8 MB memory‑side cache (MSC). The MSC buffers memory traffic and reduces latency when many cores or NPUs access RAM simultaneously.

- A ring‑bus interconnect (consistent with recent Intel CPUs) that links to the GPU and I/O tiles.

Note: Intel has used memory‑side caches before (e.g., the CrystalWell L4 cache), but the Panther Lake MSC is not comparable to Apple’s system‑level cache, which acts as a global last‑level cache for the entire SoC.

Xe3 Graphics Tile

The GPU tile measures 8.14 × 6.78 × 0.20 mm and contains:

- 12 Intel Xe3 clusters.

- 16 MB of L2 cache, implemented across eight sub‑tiles.

- The ability to disable faulty GPU clusters or cache sub‑tiles, improving overall chip yield.

I/O Tile

The I/O tile measures 12.44 × 4.00 × 0.18 mm and hosts a variety of controllers and interfaces:

- Thunderbolt 5 controller with two TB 5.0 PHYs.

- Wi‑Fi/Bluetooth controller and associated RF components.

- PCIe interfaces: one PCIe 5.0 ×4 PHY and two PCIe 4.0 ×4 PHYs.

- USB PHYs.

Because the I/O tile contains many high‑value components, it can also be binned—defective sections may be disabled to salvage the die. However, a failure in this tile often necessitates discarding the entire processor.

Additional References

- Twitter discussion of the die shots: March 5 2026 tweet

- Original die‑shot announcement on Kurnal‑Insights: