Cadence embeds AI 'super agent' to assist engineers when designing EDA tools — company aims for ‘over a trillion transistors’ by 2030, with AI helping to debug and verify complex projects

Source: Tom’s Hardware

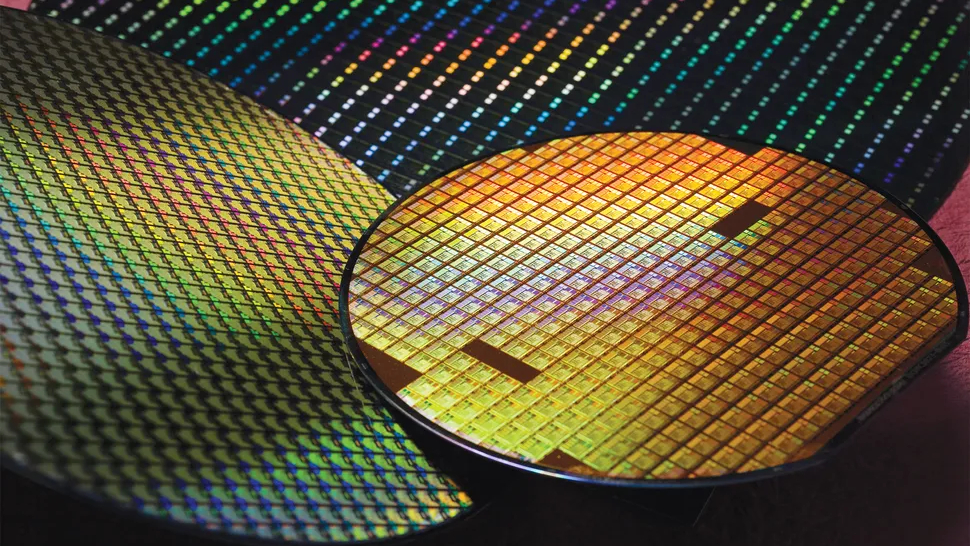

*Image credit: TSMC*

“A trillion transistors” sounds like hyperbole—until it isn’t. Designing today’s leading‑edge transistors resembles expanding a structure that never stops growing. Chiplets are bolted on as packaging stacks everything vertically, and elements like power delivery and interconnects get re‑routed each time footprints change. Eventually, the challenge of designing the actual blueprint is taken over by coordinating everything that connects to it.

That coordination is what Cadence is targeting with its new **ChipStack AI Super Agent**. Announced on February 10, the system embeds an AI‑driven assistant across Cadence’s electronic‑design‑automation portfolio, with the stated aim of helping engineers design, debug, verify, and sign off complex semiconductor projects more efficiently.

> “We’re easily going to get over a trillion transistors… in the package, by the end of the decade,” Cadence Senior Vice President Paul Cunningham said in remarks to *Bloomberg*. “It’s a phenomenal increase in complexity.”

> — [Bloomberg article (Feb 10 2026)](https://www.bloomberg.com/news/articles/2026-02-10/cadence-touts-ai-as-way-to-speed-design-cope-with-labor-crunch)Emphasis on Packaging

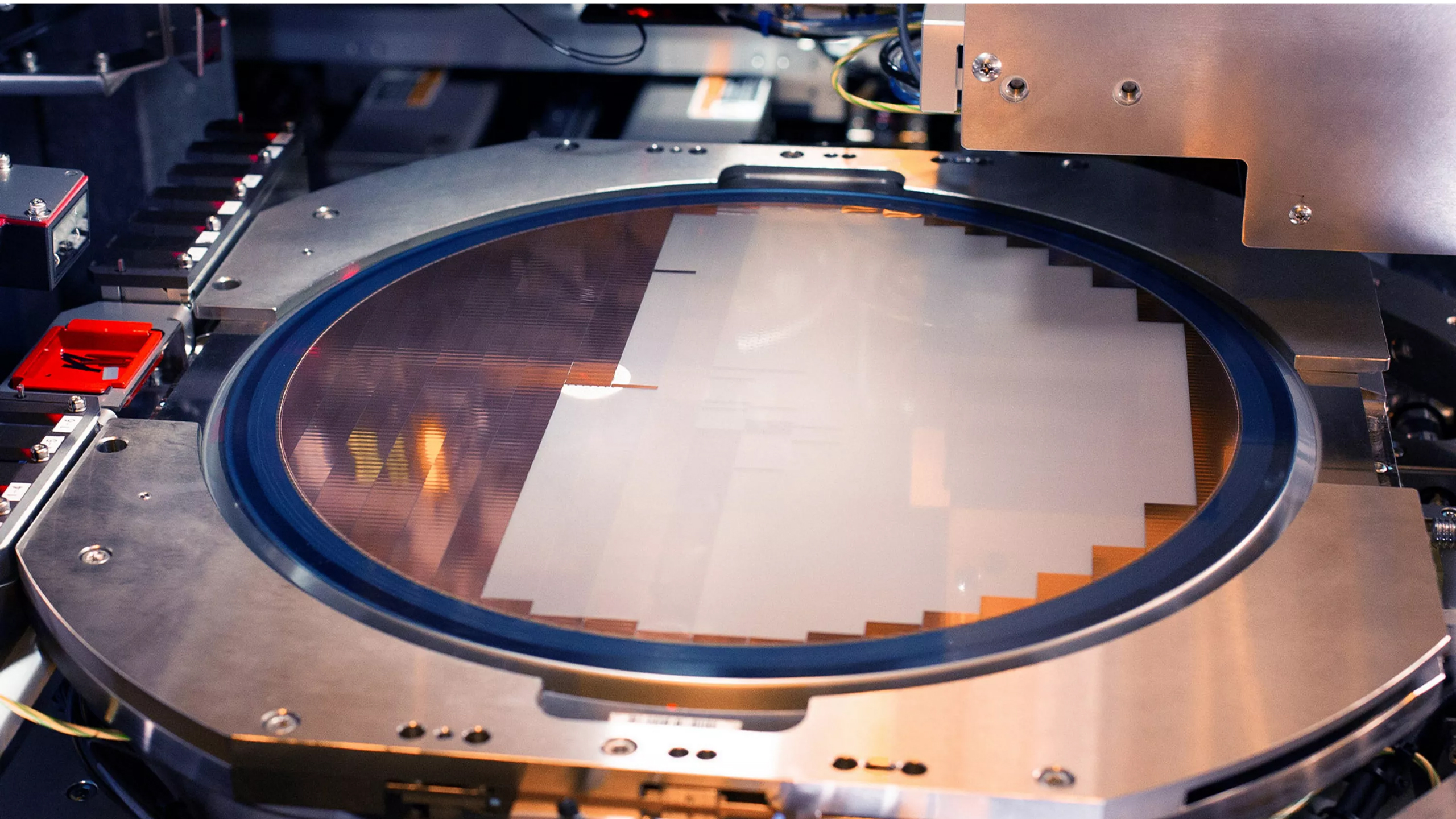

Image credit: Intel

Cunningham’s emphasis on “in‑the‑package” is significant because growth to a trillion transistors is not simply about shrinking features at advanced nodes. It also involves assembling multiple dies into unified systems through chiplets, 2.5‑D interposers, and 3‑D stacking. As architectural ambition shifts upward, the burden on design orchestration grows accordingly.

EDA has long automated the mechanics of design—synthesis, placement, routing, timing analysis, and verification are all deeply algorithmic processes that run on large compute clusters. Multi‑die packages introduce additional interconnect domains and power islands, push timing closure across die‑to‑die links, and require thermal modeling across stacked silicon. Consequently, verification is no longer isolated to block correctness; it now extends to system‑level interaction between heterogeneous components.

Engineers manage these interactions through layered tool flows, scripts, constraints, and sign‑off checks. However, reports can easily stretch into thousands of lines, and debug cycles can take weeks. Cadence’s Super Agent sits above that orchestration layer, acting as a domain‑trained AI system built on a “mental model” of chip design rather than a general‑purpose large language model. Engineers can interact with the tool stack conversationally, requesting actions without navigating every script or endless menus.

“You can chat with all of the Cadence products, and they’ll talk back to you. You don’t need to be the ultimate scripting expert. You don’t need to know all of the fancy features and tool clicks of our graphic user interfaces. You can just say, ‘Hey, look. This is what I want to do.’”

Key takeaways

- Packaging matters: Chiplet integration, interposers, and stacking are essential for reaching trillion‑transistor designs.

- Design complexity increases: Multi‑die systems add new timing, power, and thermal challenges.

- AI‑driven orchestration: Cadence’s Super Agent provides a conversational interface to streamline workflows and reduce the need for deep scripting expertise.

Labor Constraints

The Semiconductor Industry Authority (SIA) projects that the U.S. could face a shortfall of tens of thousands of industry workers by the end of the decade1. A significant portion of that gap will fall on engineers and technicians with advanced degrees. While the expansion of fab capacity under the CHIPS Act—and the resulting worker shortages—receives the most attention, design expertise is equally constrained.

Why Design Talent Is Critical

-

Advanced‑node chip design requires specialists in:

- Physical implementation

- Verification methodologies

- Packaging and signal integrity

- System architecture, among others

-

These roles demand years of specialist training and practical experience.

-

Current college and university output does not match projected demand for these skills.

The Ripple Effect on Development

- As we aim to “break the trillion‑transistor mark,” the process coordination burden grows: more blocks and interfaces → more verification scenarios → more potential failure modes.

- Without changes to workflow, the same design processes will require ever‑increasing engineering hours, making it difficult—if not impossible—to staff projects adequately.

Potential Productivity Gains

Cadence claims its Super Agent can deliver productivity improvements of up to 10× for certain repetitive, report‑heavy tasks. Even modest reductions in iteration time can compound across long design schedules, significantly accelerating development cycles.

Agentic Chip Design

Image credit: Microsoft

Generative AI has introduced uncertainty to many software categories, raising questions about whether generalized models could abstract away from specialized tools. EDA vendors operate in a tightly constrained market governed by foundry process‑design kits (PDKs) and strict sign‑off criteria. Consequently, tools such as timing analyzers and physical‑verification engines aren’t easily displaced by general‑purpose models.

Where the vulnerability lies

For decades, using EDA tools has required fluency in:

- scripting languages,

- flow configuration, and

- the idiosyncrasies of specific vendor ecosystems.

That friction has helped keep customers embedded. If an external AI assistant could sit on top of those tools and translate intent into tool commands, the interface layer would begin to loosen.

Cadence’s “Super Agent”

By embedding a domain‑trained model inside its own stack, Cadence ensures that the conversational interface is part of the platform rather than an overlay. This Super Agent doesn’t replace timing engines or verification tools; instead, it sits between the engineer and those tools, interpreting intent and mapping it onto validated flows within the Cadence ecosystem.

As architectures fragment into chiplets and stacked dies, constraints will only grow. An assistant that can interpret a designer’s request and translate it into correctly sequenced tool operations could:

- reduce misconfiguration,

- shorten debug cycles, and

- lower the coordination burden on engineers.

Industry context

Cadence isn’t alone. Synopsys and other vendors are known to be pursuing similar AI‑assisted layers across their portfolios, folding them into tool stacks to reduce coordination overhead. See the Tom’s Hardware article on Synopsys’s AI copilot: .

If Cadence succeeds in delivering a meaningful solution, it could change how teams cope with the scale described by Cunningham.

The scaling challenge

- A trillion transistors in a single package multiply interfaces, verification steps, and failure modes.

- More dies → more cross‑domain timing checks.

- More silicon stacks → more thermal interactions to model.

The coordination workload rises alongside these complexities. If the supply of advanced engineers does not expand at the same pace (), the burden must be absorbed elsewhere. Development cycles could stretch, or the effective output per engineer must increase. Cadence is trying to make the latter happen from inside the toolchain.

Luke James is a freelance writer and journalist. Although his background is in law, he has a personal interest in all things tech—especially hardware, microelectronics, and regulatory matters.